Эксперименты с Xilinx XC9572

Старое описание ковыряний с XILINX-чипами.

После экспериментов с чипами Parallax Propeller стало понятно, что штука это хоть и интересная, но по большому счету является игрушкой. Эксперименты с Propeller были остановлены и он отправился на полку собирать пыль.

Зато появилось желание наконец-таки поработать с ПЛИС и языком программирования VHDL. Конкретно для начала меня заинтересовали микросхемы производства XILINX серии XC95 (это простые CPLD) и Spartan-3 (довольно навороченные FPGA). Первая серия является скорее заменой рассыпухи, т.е. может применяться когда требуется уменьшить место, занимаемое на плате микросхемами стандартной логики, вторая же способна заменить на плате всю цифровую часть, включая микроконтроллеры.

Начинать с ПЛИС подобных XC95 проще всего: они есть в небольших корпусах (с относительно малым количеством выводов), для старта достаточно только самой ПЛИС, источника питания и простейшего программатора (иногда вообще подобие 5 проводков подойдет) для заливки конфигураций. Число циклов перезаписи в 10к тоже не доставит проблем.

Конечно, ресурсов в XC9572 очень мало. Она имеет всего 72 макроячейки. Для реализации даже самого простого универсального микропроцессорного ядра на 8 бит (PicoBlaze, к примеру), требуется более 200 макроячеек. Процессор не поместится, а вот десяток корпусов логики и хитрый дешифратор или коммутатор запихнуть в нее можно за милую душу, даже ППЗУ на 1-2кБ в помещается без особых проблем

Динамический индикатор

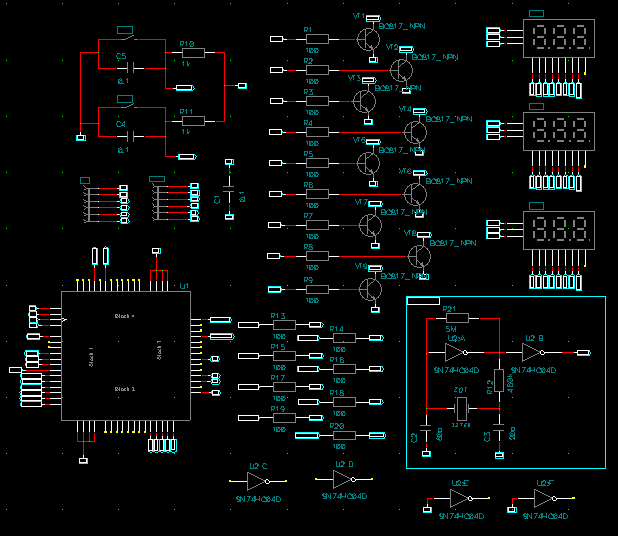

На рисунке представлена схема устройства (прошу прощения за кривоту, первый опыт рисования в P-CAD). Кроме микросхемы XC95, она включает 2 кнопки и 9 разрядов светодиодных индикаторов (3 модуля по 3 разряда), тактирование ПЛИС осуществляется генератором на элементах 2И-НЕ. Индикаторы использованы TOT-3361 (аналоги: LTM8522G и BT-N325RD), у меня они остались из старого телефона Русь.

На плате предусмотрено 2 разъема: JTAG для программирования XC95 и 6 пиновый разъем с 4мя линиями ввода-вывода. Питание платы осуществляется напряжением 3В от этого же разъема. К сожалению, плату не очень легко повторить утюгом (при разводке были установлены нормы: дорожка 0.2, зазор 0.2). Отдельно стоит отметить внешний генератор на 74HC04 с частотой 32768Гц. Он испольуется для тактирования цепей внутри ПЛИС.

Почему у генератора такая частота, а не несколько МГц, к примеру? Потому что ее проще делить и формировать интервалы в долях секунды, что требуется для часов и частотомеров, а это в свою очередь позволяет экономить ресурсы, которых и без того не особо много имеется в наличии. С генератором возникла отдельная проблема.

Предварительно я опробовал 2 версии генератора на микросхеме логики 74HC04. Первый вариант не захотел запускаться при питании от 3В (на 5В работал прекрасно). Второй же изначально подозрений не вызвал, работал на любом напряжении. Однако, после сборки на конечной плате возникла проблема: шум непонятной природы на фронтах. Единственное разумное предположение по природе шума: низкая скорость нарастания сигнала из-за низкой частоты генератора, поэтому на выходе и возникают хаотические переключения. В качестве удачного решения послужила замена 74HC04 на 74HC14 - это совместимая по пинам микросхема с 6ю инверторами, только данном случае они еще имеют в своем составе триггер Шмидта.

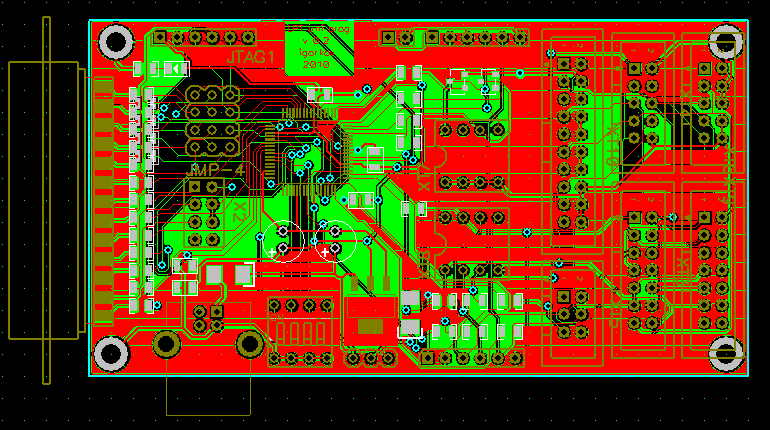

Плата разводилась автоматически при помощи Specctra:

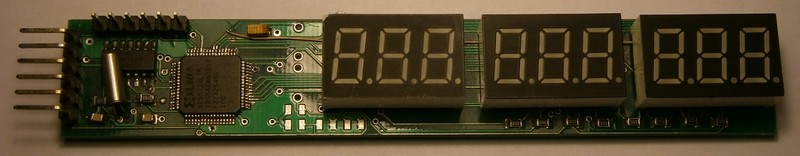

А вот конечный результат:

На плате можно заметить одну напаянную соплю: это не ошибка в разводке, а такие вот платы делает Резонит: собираю - сегмент не светится, начинаю прозванивать, в итоге понимаю, что дорожка где-то рвется. Индикатор уже был установлен, судя по всему проблема где-то под ним.

Изначально планировалось реализовать следующие демонстрации: различные варианты счетчиков, частотомер до 100МГц, примитивные часы, выносной индикатор. Однако, стало понятно, что на полноценный 9-ти разрядный частотомер ресурсов ПЛИС не хватает. Очень много требует реализация динамической индикации на 9 разрядов. В итоге, конструкция была доведена до функционирования в режиме SPI-индикатора, что меня вполне устроило.

Jtag LPT адаптор

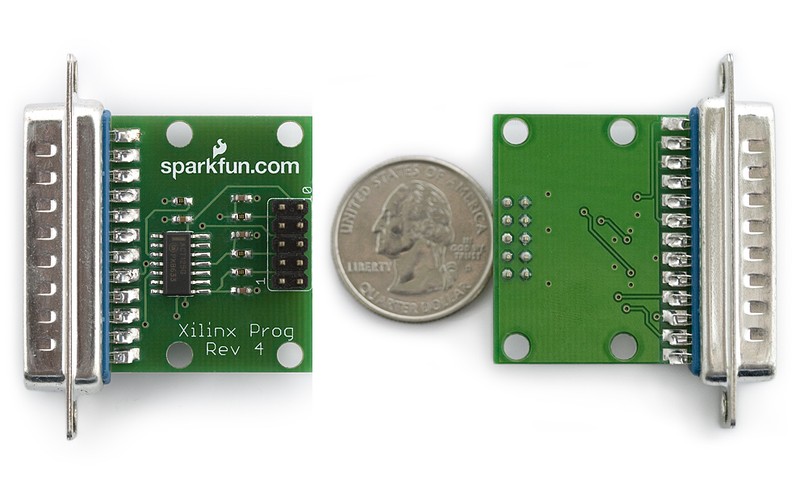

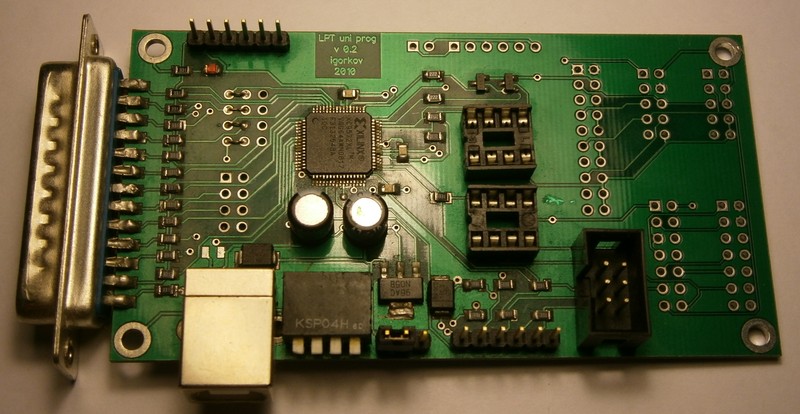

В первую очередь хочу представить обычный LPT-JTAG для ПЛИС XILINX. Схема LPT-JTAG программатора есть в официальной документации XILINX, однако с 2мя "но": схема мягко говоря избыточна и отсутствует разводка платы.

Когда я начал экспериментировать с XILINX, я собрал программатор по Reference-дизайну. Учитывая избыточность схемы, хотел было сделать еще один вариант, тем более нашлась схема и хорошая фотография платы программатора, срисовать которую нет никаких проблем:

В ней выброшен один режим функционирования, который никогда и не потребуется. Уже хотел cделать устройство, как в голову пришла одна очень интересная идея.

Универсальный LPT-адаптор

Можно сделать программатор для XILINX. Если требуется можно сделать другой программатор, например, STK200. Не сложно найти варианты отладчика Wiggler, предназначенного для чипов с ядром ARM. Если требуется MSP430, то пожалуйста, производитель распространяет схему простого отладчика для него. Большинство современных программируемых чипов имеют простые варианты программаторов и/или отладчиков для LPT-порта. В большинстве своем они отличаются только используемыми пинами разъема LPT и включают в себя один буфер на подобии 74HC244.

Отсюда возникает вопрос: а зачем делать кучу устройств, если можно один раз собрать чуть более сложное и использовать его для всего? Такое универсальное устройство не окажется лишним, так как порой натыкаешься на интересную конструкцию, а она оказывается на PIC-микроконтроллере (а инструментарий есть только для AVR, к примеру).

Основная идея в том, чтобы установить в качестве "сердца" программатора ПЛИС. Подключить к ней дип-переключатель, в зависимости от состояния которого будет выбираться режим работы. ПЛИС будет реализовывать различные варианты коммутации LPT и пинов ISP/JTAG-разъемов, одновременно с этим ПЛИС является буферным элементом. Таким образом можно совместить в одном устройтсве несколько программаторов/отладчиков для LPT-порта. ПЛИС в данном случае будет выполнять функции довольно сложного мультиплексора.

Конкретно, у меня получился такой список эмулируемых LPT-устройств:

- JTAG Wiggler

- STK200/300

- ALTERA ByteBlaster

- XILINX JTAG

- TMS320 JTAG (клон OLIMEX-варианта)

- MSP430 JTAG

- PIC ICSP

- SPI EEPROM MEMORY

- I2C EEPROM MEMORY

Предусмотрены разъемы:

- ARM JTAG 20-pin

- STK200/300

- 2x3 AVR ISP

- 2x5 AVR ISP

- 2x7 TMS320

- 1x6 XILINX

- 2x8 MSP430

- 1x6 PIC ICSP

- ALTERA 2x5

- SPI MEMORY DIP-8

- I2C MEMORY DIP-8

Режимы работы задаются DIP переключателем и включают в себя:

| 0000 | RFU / Самопрограммирование. |

| 0001 | JTAG Wiggler, 20 pin PLD connector. |

| 0010 | STK200/300, 6 pin PLD connector or 10 pin PLD connector. |

| 0011 | RFU / ALTERA ByteBlaster. |

| 0100 | XILINX JTAG 6 pin PLS connector. |

| 0101 | RFU / XDS510PP (TMS320 JTAG) 14 pin PLD connector. |

| 0110 | MSP430 JTAG |

| 0111 | PIC ICSP, 5 pin PLS connector. |

| 1000 | SPI EEPROM MEMORY DIP-8 connector. |

| 1001 | I2C EEPROM MEMORY DIP-8 connector. |

| 1010 | RFU |

| 1011 | RFU |

| 1100 | RFU |

| 1101 | RFU |

| 1110 | RFU |

| 1111 | RFU |

Согласитесь, очень не мало. Схемотехнически можно предусмотреть все разъемы, которые потребуются, но вот реализовать все это разом сложно, особенно не имея половину устройств из списка для проверки (а для отладчика OLIMEX для TMS320 даже схемы нет, так что он выходит RFU).

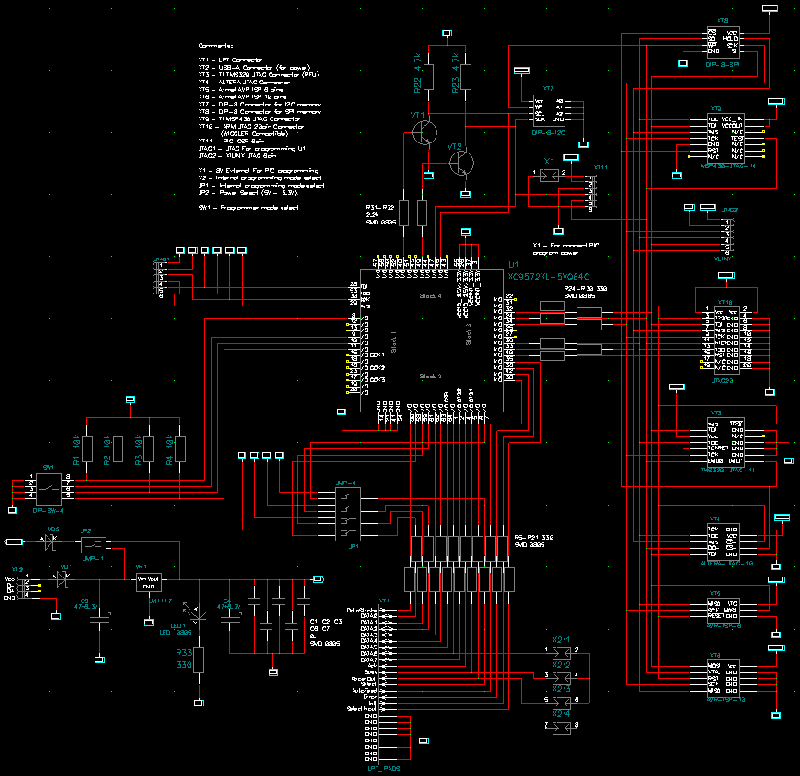

На рисунке ниже представлена схема устройства. Как можно заметить, микросхема ПЛИС является центральным связующим звеном между LPT-портом и всеми разъемами. Единственные внешние активные компоненты -- это пара транзисторов для реализации включения с открытым коллектором. которое требуется для I2C шины и программирования PIC-ов.

Прошу не плясать от счастья увидев разъем USB, он предусмотрен только в целях подачи питания, в случае отсутствия такового на JTAG/ISP разъеме. С питанием связана еще одна важная особенность: джампер 1. Он выбирает напряжение питания. В случае питания от USB его устанавливать не требуется, а вот в случае питания от JTAG-ISP разъемов он очень важен. При подаче с разъема программирования 3.3В все нормально, оно годится для запитки ПЛИС, а вот в случае питания целевой платы напряжением 5В и наличием на разъеме программирования этого напряжения, джампер обязательно требуется установить в положение 5В, переключив на понижающий стабилизатор.

Джампера 2-5 и 6-8 предназначены для решения проблемы "курицы и яйца". При перестановке их в положение PROG, можно запрограммировать ПЛИС самого программатора при помощи стандартного инструментария XILINX (утилита iMPACK). Однако вместо них можно распаять перемычки и программировать ПЛИС обычным способом, через отдельный JTAG-разъем, так же предусмотреный на плате.

А вот и вид самой платы:

Итоговая экономия на таком устройстве, думаю, ясна всем. Стоимость всех необходимых комплектующих (кроме платы) получается в районе 300 рублей, а готовый серийный LPT-программатор для чего-то одного стоит от 500 руб.

XILINX Jtag Player

У XILINX есть несколько интересных Application Notes по заливке конфигураций через JTAG при помощи микроконтроллеров. Изучение данного материала и прилагаемого кода показало, что можно без особых затрат создать так называемый JTAG-плеер. Что это такое? Это устройство, посылающее в JTAG последовательность команд, результат которых какие-либо дейтсвия, если конкретно: прошитая FLASH-память контроллера (даже внешняя), прошитая конфигурация ПЛИС (или прото загруженная для FPGA). Довольно заманчивая возможность.

Код, предоставляемый XILINX в апноуте, написан с явно выделенным уровнем абстракции от железа и операционной системы и легко переносится. Вместо LPC2100 можно без проблем использовать любой другой микроконтроллер и даже хранить весь XSVF файл внутри микроконтроллера или на непосредственно подключенной памяти. Единственный замеченный недостаток: буфера приличного (по микроконтроллерным меркам) размера, используемые внутри кода, но они без проблем уменьшаются.

Конечно, при помощи такого механизма можно сделать USB-программатор для XILINX, но работать он будет через специфичные утилиты. Подобный механизм загрузки по JTAG интересно использовать, к примеру, с FPGA-чипом для загрузки конфигурации из микроконтроллера, без использования дополнительных чипов памяти.

Разработка

Среда для разработки - Xilinx ISE WebPack, распространяется бесплатно. Изначально я выбрал для себя разработку на VHDL, хотя по ходу дела попробовал порисовать графически. При разработке на VHDL все-таки желательно знать, каким образом функционируют триггеры, какая внутренняя структура у мультиплексора, дешифратора, регистра и прочие схемотехнические особенности. Иначе, можно описать ТАКОЕ, что в принципе синтезу не поддается, а это сделать на VHDL проще простого.

Примечание: В программировании ПЛИС не используется понятие "компиляция", оно заменено понятием "синтез", причем процесс синтеза занимает существенно больше времени. По началу это нервирует, особенно если есть привычка контролировать синтаксис кода путем компиляции проекта.

Небольшой объем ресурсов и простые обкатываемые схемы заставляют постоянно контролировать, что синтезируется из описания.

Отладка

Для отладки можно осущетсвить 2 подхода. Первый - это непосредственное тестирование в железе, т.е. циклично заливаем описания, смотрим что некорректно работает, правим и снова заливаем. Процесс не быстрый и очень неэффективный.

Второй способ - использование симулятора. Причем отладка в нем организуется следующим образом: создается некая архитектура/компонент. Разработчик знает каким образом он должен функционировать. На основе этого, он создает тестовый модуль, так же на VHDL, который подает различные комбинации импульсов. В простейшем случае можно напрямую протестировать блок, но только в простейшем, так как сигнал такта в тесте всего один.

В общем, процесс отладки не очень приятный и быстрый. В любом случае, из-за особенностей архитектуры ПЛИС, отлаживать их наподобии микроконтроллеров нельзя: здесь нет единой ветки исполнения, и не получится поставить точку останова.